|

|

楼主 |

发表于 2017-1-14 17:03:11

|

显示全部楼层

本帖最后由 兰陵月 于 2017-1-14 17:35 编辑

不知道你基础怎么样,我就大概说说吧,那只是用来说明如何做出地址空间吧,你有注意到是同一条线接到8个锁存上面吗,没有在写操作端加译码器那就是一次就把8个锁存的状态都改成了1 或0,【理解,因为没有选择电路,所以要么都是1,要么都是0】

如果第一个是地址1,第二个是地址2....,那这时要求你把0写入地址6 ,你就只能加装译码器阿,让写操作端只有在第6个是通路,读取亦同。

【理解,因为没有这个译码器,就不能指定选择某一个位】

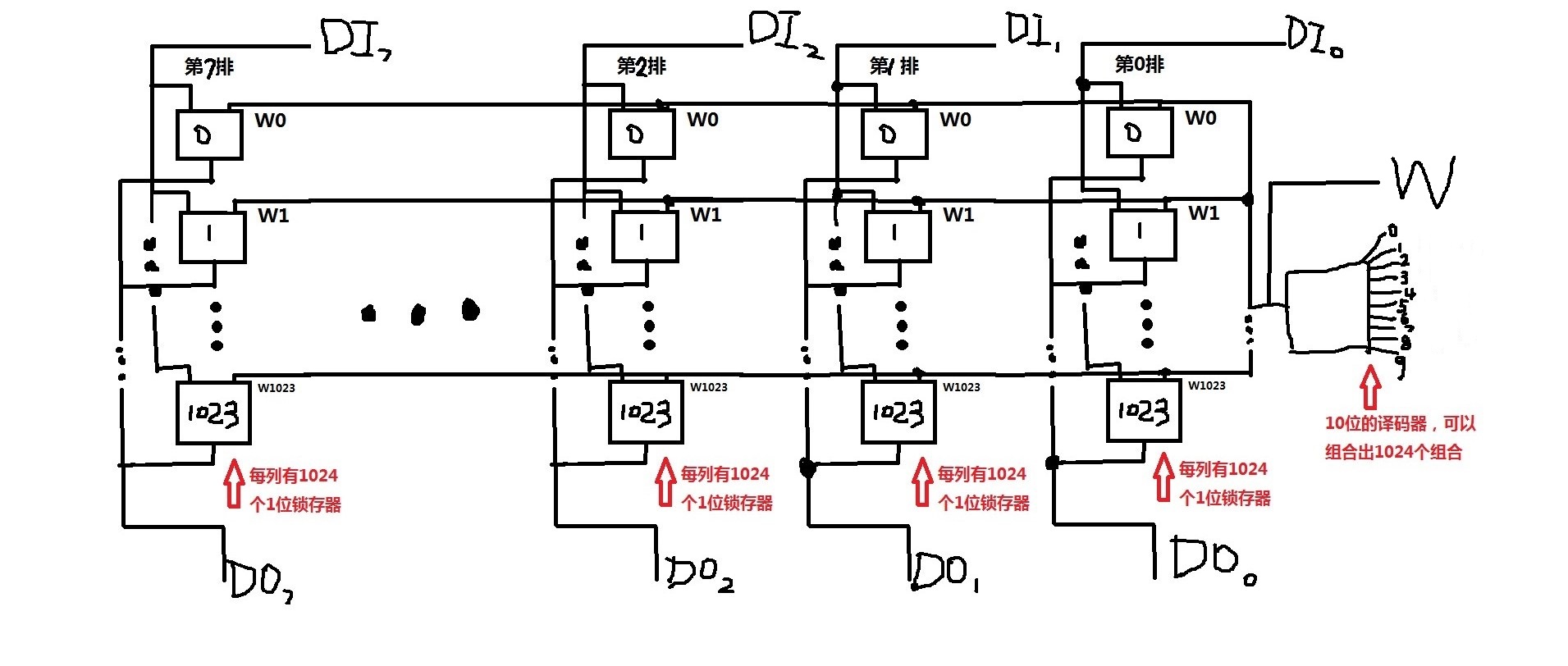

这时你可以扩增每个地址所能存放的容量,先假设你要做出1024*8 bit 的ram,那你需要10个地址线做出1024种可能,接到1024个1bit锁存,这时地址总数有1024个,但容量是1bit,【理解】若要写入数据到某某地址,可以先把数据输入改成你要写入的值,把地址配置成让某某地址的写操作端是通路,再把写操作端置1置0就完成了,【理解】这时你只要再并排多弄出7个这样的结构,不同之处是这另外7个的数据输入端是个别独立的,这样当你让某个地址是通路以写入时,就是一次写8个个别的数据进去,这样就完成1024 *8 bit 的ram。【下图就是我的理解~~这样会导致每行的数据都是一样的啊】

我这样理解是正确的吗????把我这个图右旋转90度,是不是就是和你的一样?只不过你的是8个地址,我的是1024个地址?

W线最后共用部分可能不是这样画的,但是意思是译码器数据不同,就开放某个W信号,允许对某个锁存器读写。 |

|

( 粤ICP备18085999号-1 | 粤公网安备 44051102000585号)

( 粤ICP备18085999号-1 | 粤公网安备 44051102000585号)